목차

1.MOSFET

2.단일 증폭기

3.캐스코드, 전류미러

4.차동 증폭기

5.주파수 응답

6.피드백

1.MOSFET

# 왜 MOSFET이 증폭기를 만드는 데 사용될까?

도체는 저항이 작고, 부도체는 저항이 크다 → 반도체는 저항을 '조절' 할 수 있다 → '전압'으로 저항을 조절한다 → '전압'으로 전류를 조절한다

전압 증폭기(CS AMP) 고려하면,

입력 전압 → MOSFET → id = gm·vgs → R → 출력 전압

참고로 id = gm·vgs에서 vgs(입력 전압 변화)가 소신호일 때 id = gm·vgs처럼 선형근사를 할 수 있다

결론적으로 입력 전압의 변화를 증폭시켜 출력 전압의 변화를 만드는 것이다 (vout = 0 - gm·vgs·RD)

# NMOS vs PMOS

NMOS : 전류를 형성하는 캐리어가 '전자' → n+ source, drain & 자유전자로 channel 구성되어야 ON → VG가 클 때 ON

PMOS : 전류를 형성하는 캐리어가 '정공' → p+ source, drain & 정공으로 channel 구성되어야 ON → VG가 작을 때 ON

NMOS : Substrate는 p- → VG가 작을 때 OFF

PMOS : Substrate는 n- → VG가 클 때 OFF

NMOS, PMOS 모두 입력 전압이 커지고 작아짐에 따라 Steady Region → Depletion Region → Channel Region

아래는 NMOS, PMOS의 표시이다

1. 전류는 전압이 높은 쪽에서 낮은 쪽으로 흐른다

2. NMOS에서는 D > S이고 PMOS에서는 S > D이다 → 모두 위에서 아래로 전류가 흐른다

3. Source에 전류 방향을 표기한다

4. 보통 B는 S(가장 높은/낮은 전압)와 연결(∵ blocking junction leakage)

# MOSFET 전류식과 동작영역

아래 그림은 다양한 동작영역에 따른 MOSFET의 전류식이다

1.Cutoff 영역

channel X → IDS X

2.Deep triode 영역 (VGS 고정일 때 '저항')

VDS(MOS의 양단 전압)가 매우 작다 → VGS를 따르는 가변저항에 따라 IDS 결정 → VDS = IDS·Ron(linear)

3.Triode 영역

4.Saturation 영역 (VGS 고정일 때 '전류원')

VDS 크다 → channel을 형성하는 자유전자들이 drain으로 이동 → channel이 끊기는 pinch-off 발생 → 이상적으로는 전류가 VDS에 따라 변화하지 않는다(VGS 의존) → VDS가 증가함에 따라 자유전자들이 drain으로 더 많이 이동 → effective channel length(L')가 점점 짧아진다 → 실제적으로는 전류가 VDS에 따라 변화한다

아래는 채널 길이에 따라 channel length modulation의 영향의 차이이다

기존의 채널 길이가 짧으면 channel length modulation 효과가 더 커져서 VDS에 따라 전류가 더욱 급격히 증가한다

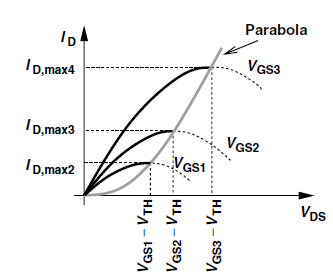

동작모드에 따른 드레인 전류를 그래프로 정리하면 아래와 같다

Triode 영역은 선형영역이라 불리는 것처럼, ID가 VDS에 선형적이다(저항 역할)

Saturation 영역은 전류원 역할을 한다

아래는 VGS에 따라 결정되는(Carrier 농도 결정) 최대 전류(Saturation 전류)에 대한 그림이다

VGS가 크면 Carrier 농도가 커져서 최대 전류가 증가하게 된다

왼쪽 그림의 약한 회색선은 최대 전류의 집합으로써 saturation 영역에서의 전류이고, VGS-VTH를 X축으로 해 그린 것이다

아래는 소신호 저항을 고려한 Saturation 전류식이다

Channel length modulation에 의해서 vds(전압 변화)가 id(전류 변화)에 기여하고, 이를 소신호 저항으로 모델링 할 수 있다

결과적으로 소신호 저항은 Saturation 영역에서 Channel length modulation 효과를 반영하기 위한 수단이다

실제적으로 소신호 저항은 실제로 존재하는 것이다

다만 VGS 변화로 인한 ID의 변화(gm 크다)에 비해서

VDS 변화로 인한 ID의 변화(gm0는 r0가 크기 때문에 작다)가 작기 때문에 대신호적으로 크게 고려하지 않는 것이다

즉, r0(100)가 크기 때문에 VDS의 변화가 크더라도(10%) ID의 변화는 0.1% 밖에 안되는 것이다

※왜 MOSFET 증폭기를 만들 때 Saturation 영역만 사용해야 하는가?

증폭의 원리인 '입력 전압 변화 → MOSFET → 전류변화 → R → 출력 전압 변화'를 고려한다면, MOSFET의 전류 변화가 오직 입력 전압 변화(vgs)에만 의존하고 출력 전압 변화(vds)에 의한 영향을 최소화하기 위해서는 MOSFET을 활용한 증폭기를 만들때 반드시 saturation 영역을 사용해야 한다

또한, triode 영역에서 입력 전압 변화가 더 큰 출력 전압 변화를 만들어 낼 수는 있지만 출력 전압 변화(vds)의 영향을 많이 받고, 소신호 관점에서 saturation 영역과 달리 선형근사를 할 수 없다

아래는 saturation 영역을 쉽게 Biasing 하는 방법인 Self-biasing 회로이다

왼쪽 그림은 사람이 Biasing을 조절해야 하지만, 오른쪽은 자동으로 Saturation 영역을 만족시키고 전류도 구할 수 있다

아래에는 gm식을 첨부한다

2.단일 증폭기

#단일 증폭기 종류

CS, CS+Rs, CG, SF

#특징

| Single Amplifier | Voltage gain | Input Impedance | Output Impedance | Comments |

| CS | High | High | High | 전압 잘 받는다 (전압 증폭기) |

| CS+Rs | Medium & Stable | High | High | Negative feedback을 CS에 추가한 것 |

| CG | High | Low | High | 전류 잘 받고, 잘 준다 (전류 버퍼) |

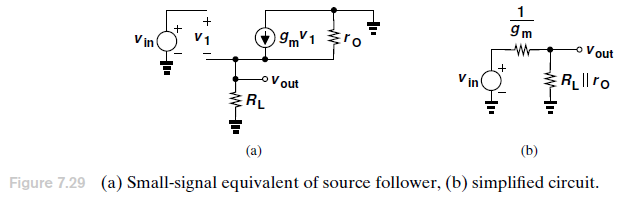

| SF | 1 | High | Low | 전압 잘 받고, 잘 준다 (전압 버퍼) |

CG는 전압 이득은 크지만 입력 임피던스가 작아서 전압을 잘 받지 못해 전압 증폭기로 잘 사용되지 않는다

SF를 CG 앞에 두더라도 SF의 출력 임피던스도 1/gm이고 CG의 입력 임피던스도 1/gm이라서 전압을 그리 많이 받지는 못한다

아래에서는 차례대로 CS, CS+Rs, CG, SF에 대해 간단히 살펴보겠다

왼쪽 그림에서 saturation을 만족시키기 위해서는 VD > VG-VTH이므로 출력 파형의 최소값이 VG-VTH보다 커야함을 표시한 것이다

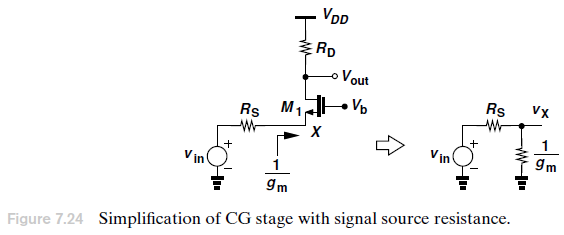

CG의 source에 Rs가 있는 경우, CS에 degeneration을 했을 경우와 부호만 다르고 전압 이득은 같다

#Path adding 개념

CS AMP로 고려 : VGS가 증가하면 MOS가 만들어내는 saturation 전류(CLM X)가 증가한다 & '출력전압 감소' → 소신호 저항에 흐르는 전류 감소 & RD에 흐르는 전류는 증가 → 기존에는 RD에 모든 전류 변화가 반영되어 출력 전압의 변화를 만들었다(id = gm·vgs) → 소신호 저항이 추가되면(path adding) 전류 변화를 뺏어간다(소신호 저항이 없다면 RD의 전류 변화는 id=gm·vgs 일텐데 소신호 저항이 있어서 이보다 감소한다) → 출력전압의 변화 감소 → Gain 감소

이러한 Path adding 개념은 다음 stage의 입력저항으로도 고려가 가능하다

CS AMP의 다음 단 회로의 입력 저항이 작다면 전류 변화를 다 뺏어가 전압이득이 작아질 것이다

반면에 입력 저항이 크다면 전류가 다음 단으로 잘 흐르지 않기 때문에 전류 변화를 뺏어가지 않아 CS AMP의 전압이득이 커질 것이다

#CS에 Rs를 추가하는 이유

장점

증폭기 관점 : VG가 바뀌어도 VGS(MOS의 입력 전압)이 덜 변한다(Negative feedback) → Bias point의 안정성

전류원 관점 : 출력저항 증가 → 외부 전압 변화에도 전류변화X

단점

Gain 감소

하지만 Gain 감소는 bypass capacitor를 추가함으로써 해결 가능

→ large signal : Rs 존재해 Bias point의 안정성 확보, small signal : Rs 존재하지 않아서 Gain 증가

#Gain이 1인 SF를 사용하는 이유 → Real gain!!

앞 단에 CS AMP가 있는 경우, Gain이 gm·RD이고 출력저항이 RD이다

다음 단에 전압 변화를 크게 전달하고 싶은데 출력저항이 RD로 크고 다음 단의 입력 저항이 작으면 Gain이 gm·RD로 크더라도 적은 전압 변화를 전달할 수 밖에 없다

이를 해결하기 위해서 RD를 줄이자니 기존의 Gain을 포기해야 한다

그 두 회로 사이에 SF를 사용하면, SF는 입력저항이 크기 때문에 앞단이 전달하고 싶어하는 전압 변화를 모두 받을 수 있고 출력저항이 작기 때문에 뒤의 회로의 입력저항이 작더라도 최대한 많은 전압 변화를 전달할 수 있다

실질적으로 Gain은 gm·RD으로 이전과 동일하지만, stage 간의 저항 dividing 으로 깎이는 전압 변화를 막는 역할을 수행함으로써 앞 단이 열심히 만든 큰 전압 변화(전압 이득 gm·RD)를 다른 회로로 온전히 전달할 수 있다

3.캐스코드, 전류미러

#좋은 전류원이란?

이상적인 전류원 → 어떤 상황에서도 전류 일정

출력저항 무한대라서 한쪽의 전압이 변해도 전류가 변하지 않는다

아래는 MOS 전류원(Saturation)이다

이상적인 전류원과 달리 MOS 전류원은 출력저항이 무한대가 아니기 때문에 A 전압이 변화하면 전류가 변한다

이를 개선하기 위해서는 출력저항을 증가시킬 필요가 있다

#MOS의 출력저항을 어떻게 증가시킬 것인가?

1.Source degeneration

Rout = ro → Rout = Rs + ro(1+gmRs)

하지만 Source degeneration은 source 쪽 IR drop이 존재한다 → 다른 회로의 전압 범위를 줄인다

MOS 전류원을 Saturation 영역에 존재시키기 위한 VD의 전압이 증가하게 되고 VDD에 대해서 다른 circuit의 전압 범위를 줄인다

이를 해결하기 위해서는

Small signal : 큰 Rout

Large signal : 작은 IR drop

→ Cascode!

2.Cascode

Cascode를 통해

Small signal : 큰 Rout

Large signal : 작은 IR drop

을 이루어 낼 수 있었다

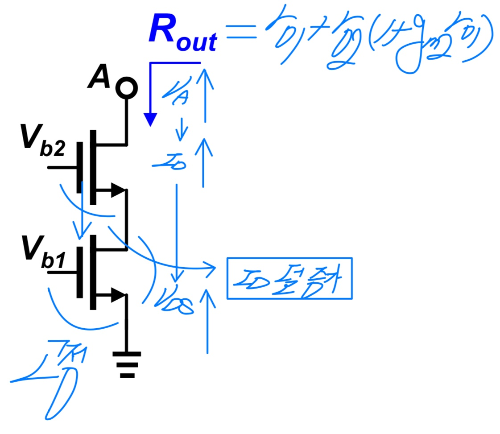

아래는 Cascode 도입을 통한 전류원의 출력저항 증가를 나타낸 것이다

large signal까지 확인했으니 이러한 cascode 구조는 한번에 처리하자

#출력저항이 큰 것이 좋은 것인가?

전압을 전달하는 관점에서는 좋지 않다 → 다음 단의 저항이 작다면 전압을 적게 전달

전류를 전달하는 관점에서는 좋다 → 다음 단의 저항이 작다면 전류를 많이 가져간다

출력 전류를 고려함에 있어서 출력 저항이 클수록 전류를 다음 단에 많이 전달한다

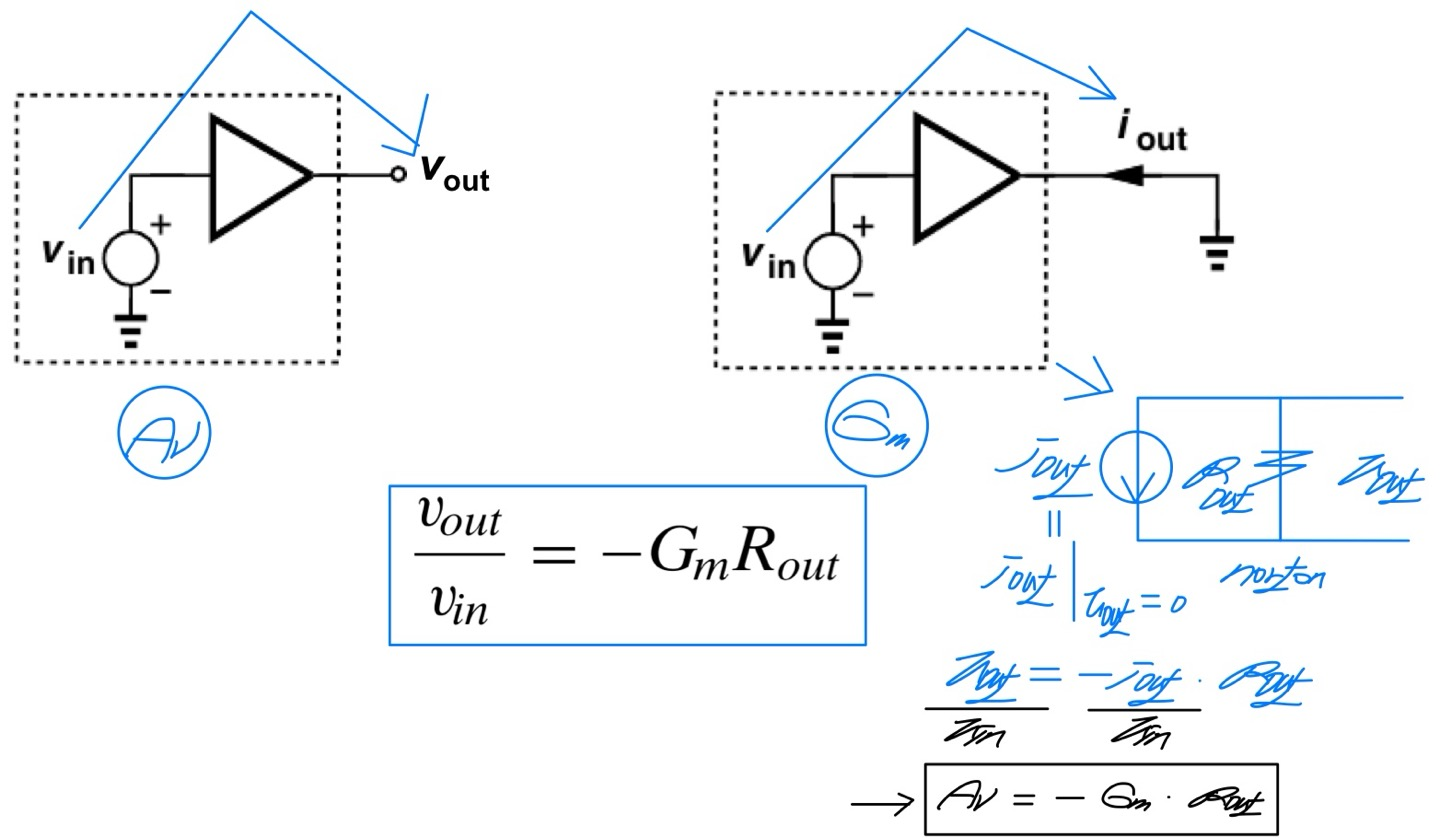

위의 질문에 대한 해답을 얻기 위해

먼저 Av와 Gm의 관계를 살펴가고자 한다

입력 전압에 대해서 회로가 만들어 내는 전류

큰 Rout은 다음 단에서의 저항 dividing에 의한 전압 손실이 존재하지만, Av가 증가하기 때문에 결국 Gv가 증가한다

출력저항이 커서 Voltage dividing을 고려하면 다음 단에 열심히 만들어낸 큰 전압 변화(전압 이득)를 전달하기 어려울 수 있다

이러한 출력저항이 큼으로 인해 다음 단에 전압 변화를 잘 전달하지 못할 것 같은 문제는 Source follower를 사용해 해결할 수 있다

Source follower는 입력 저항이 매우 커 앞 단의 전압을 잘 받을 수 있고, 출력 저항은 매우 작아 뒷 단의 입력저항이 작아도 큰 전압 변화를 전달할 수 있다

#전류원을 일일이 다 만들어야 하는가?

전류 미러를 사용하면 Bandgap reference circuit에서 만들어낸 강건한 전류를 여러 곳에 사용할 수 있다

4.차동 증폭기

#왜 차동 증폭기를 사용할까?

단일 증폭기에서는 VDD를 기준으로 전압의 변화가 고려되는데

만약 기준인 VDD가 흔들린다면 출력 전압의 변화가 흔들리게 된다

차동쌍을 이용하면 VDD가 출력에 영향을 미치지 않기 때문에 차동쌍을 활용한 차동 증폭기를 사용한다

#차동 증폭기의 기본 원리

VCM은 두 입력의 공통 모드 전압(DC 전압)이다

두 입력에서 다른 점은 AC 전압이다

위의 그림에서 Tail current source가 고려된 것이 아래의 차동 증폭기의 기본 구조이다

대칭에 의해서 전류는 절반으로 나뉘어 유지된다(ISS/2 고정)

P node는 VCM이 변경되거나, ISS가 변경됨에 따라서 자동으로 변경된다

Vin1-Vin2(차동 입력)이 차동 증폭기의 입력이다

Vx-Vy(차동 출력)이 차동 증폭기의 출력이다

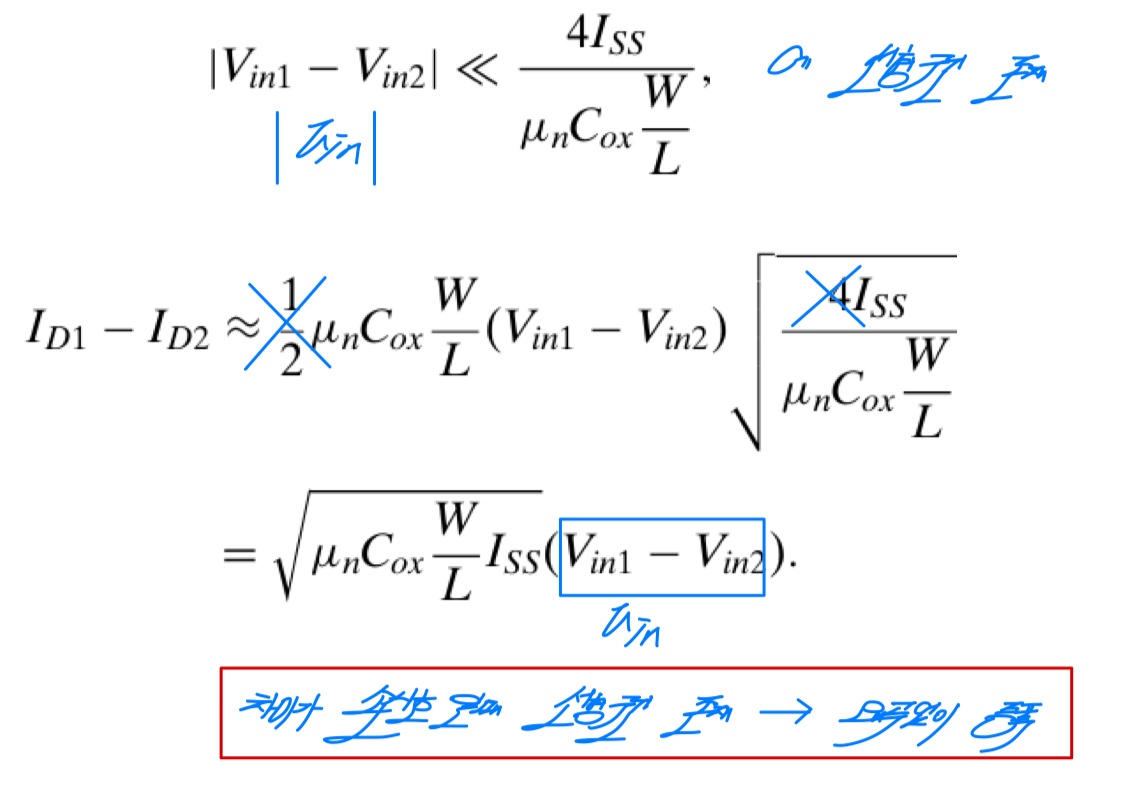

차동 증폭기도 단일 증폭기와 마찬가지로 차동 입력이 소신호 일 때 차동 출력이 차동 입력에 대해서 선형적이다

이 전류식에 RD를 곱하면 전압이득 gm·RD이다

차동 입력이 소신호 일 때 위와 같은 전압이득이 나온다

※P node는 왜 그냥 ground도 아니고 virtual ground일까?

왜 virtual ground일까?

대신호 관점에서는 전압이 변할 수 있지만 소신호 관점에서는 전압 변화가 거의 없어서 virtual ground로 고려한다

이 때 대칭인 지점이 virtual ground이다(저항이 있다면 저항을 절반으로 나눈 지점)

대신호 전압은 0이 아니다(이전에 고려한 saturation 식에 의해서 결정된다)

소신호 전압은 virtual ground → 소신호 모델에서 ground로 고려한다

#Cascode 차동 증폭기

#CMRR(Common Mode Rejection Ratio)

1.이상적인 경우(ACM = 0)

VCM.IN(입력 DC)가 변화 → 드레인 전류 ISS/2로 일정 → Bias current를 변화시키지 않고 P node가 VCM을 따라 간다

Bias current(드레인 전류)가 변하지X → VCM.IN이 VCM.OUT(출력 DC)에 영향X

ACM = △VCM.OUT / △VCM.IN = 0 (입력 DC의 변화가 출력 DC의 변화에 영향X)

2. RSS 존재(ACM ≠ 0, ACM-DM = 0 → CMRR이 무한대)

VCM.IN이 변화 → P node 변화 → RSS를 통한 Tail current 전류 변화 → Bias current 변화 → VCM.IN이 VCM.OUT의 변화에 영향을 끼친다

ACM = △VCM.OUT / △VCM.IN ≠ 0

그러나 차동 출력의 변화에는 VCM.IN이 영향X

Large signal : VCM.IN의 변화로 인해 VCM.OUT 변화 → ACM 존재

Small signal : gm이 변하더라도 같은 양으로 변화한다

차동 출력 VOUT = VOUT1-VOUT2

ACM-DM = | △VOUT / △VCM.IN | = 0

1,2 번에서는 VCM.IN이 차동 출력 VOUT에 영향을 끼치지 못한다 → VCM.IN에 의한 △VOUT는 unsymmetry가 있어야 생긴다

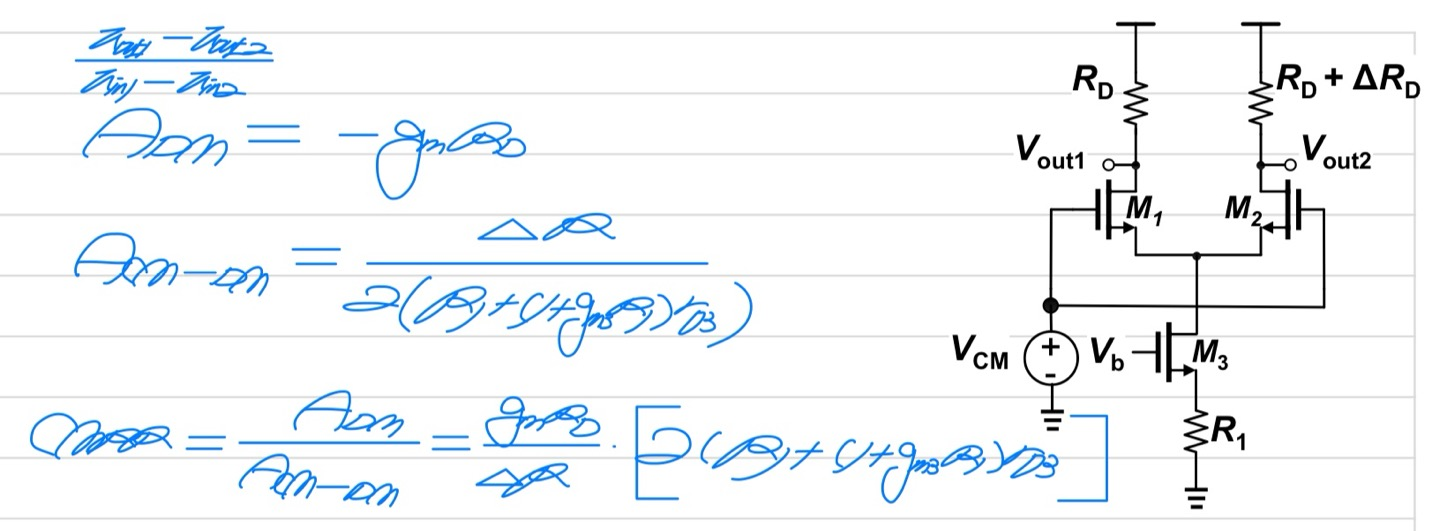

3.저항 Mismatch 존재(ACM ≠ 0, ACM-DM ≠ 0 → CMRR이 무한대가 아니다)

CMRR은 클수록 좋다

ADM은 클수록 좋고, ACM-DM은 작을 수록 좋기 때문이다

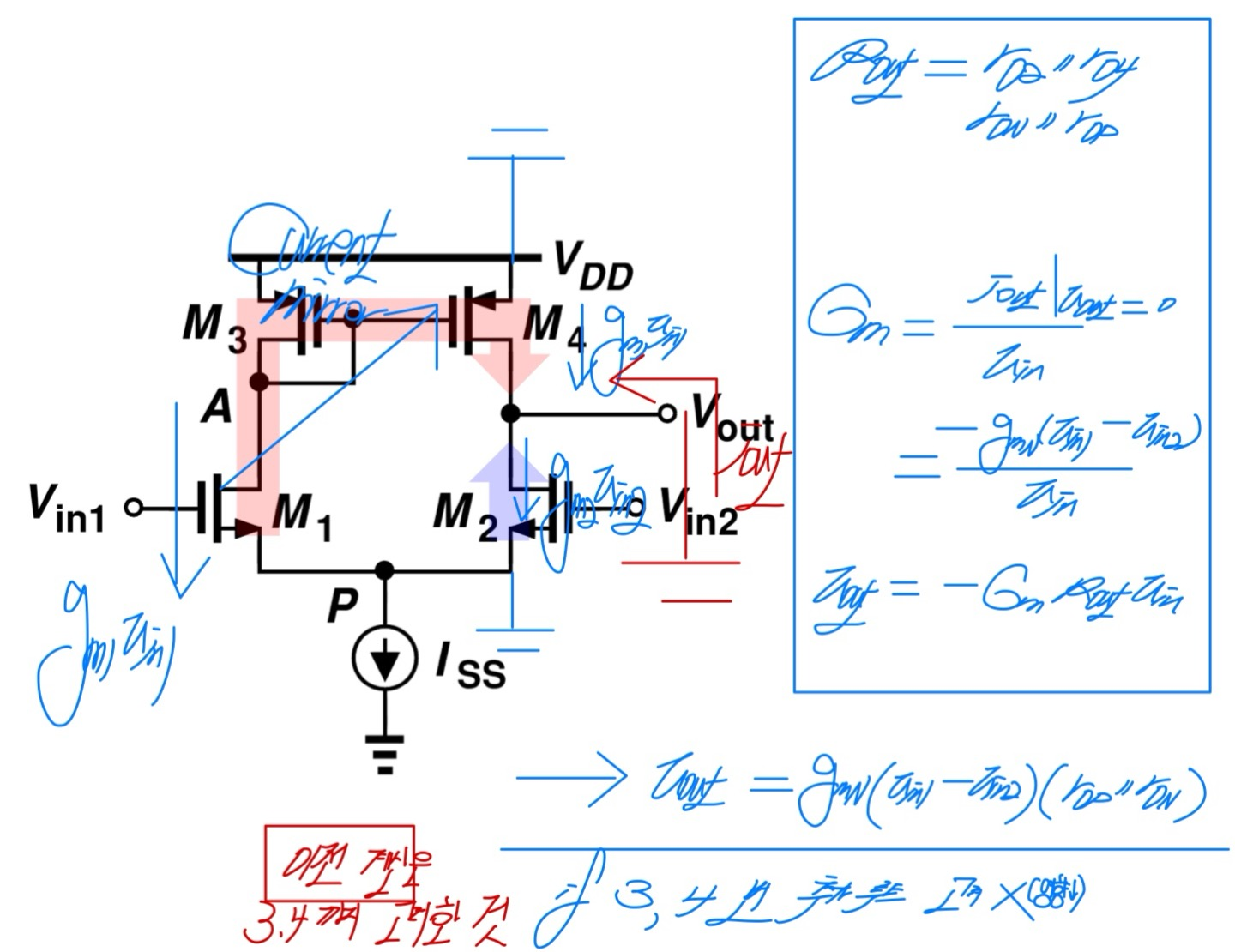

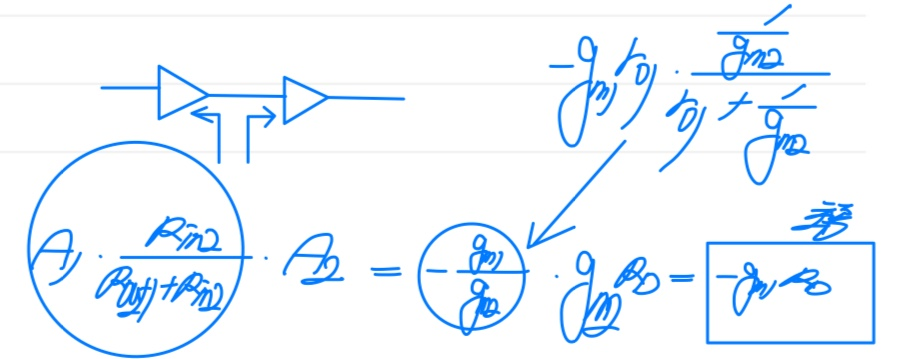

#Active Load 차동 증폭기

왜 Active Load 차동 증폭기를 사용할까? → Single-ended output을 만들기 위해서!

4개의 경로를 고려해서 등가회로를 구한 뒤, Gain을 구하면 아래와 같다

2개의 경로를 고려해서 Gain을 구하면 아래와 같다

5.주파수 응답

#Capacitor의 특징

주파수 응답에서는 주파수에 따라 변화하는 회로를 설명하고자 하는 것이다(Gain, Phase)

이러한 주파수 응답은 Capacitor의 영향으로 일어나게 된다.

교류신호에서 Capacitor에 대해서 전압과 전류를 고려해보면, 전류의 페이즈가 전압의 페이즈보다 90도 빠르다

이 말인 즉슨, 전압이 변화를 시작하기 전에 이미 전류는 변화를 시작했다는 것이다

전류의 흐름보다 전압의 변화가 느리다는 것이다

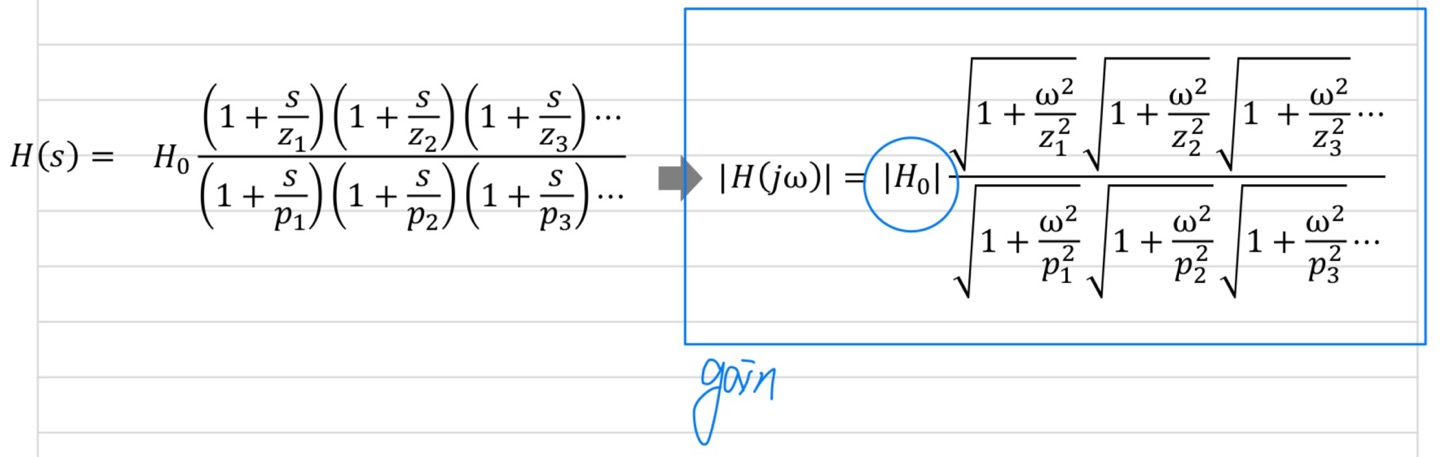

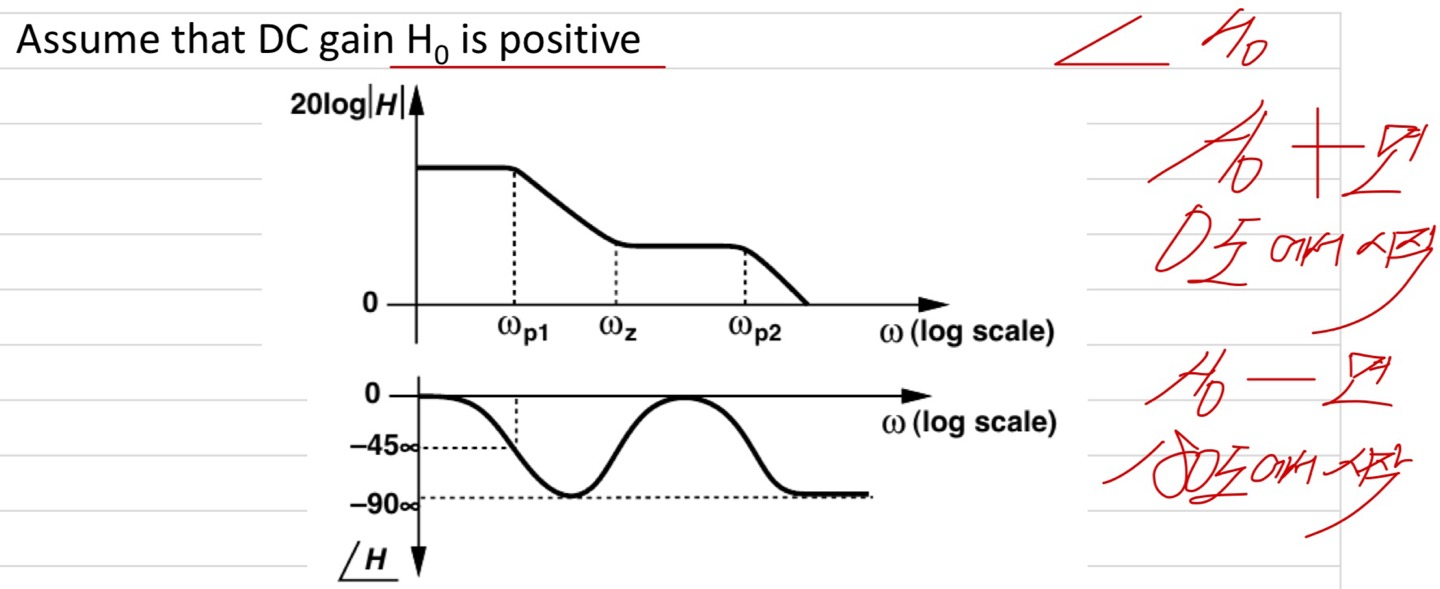

#Bode Plot에서 폴과 제로 고려하기

Bode Plot : 20log10H

분모, 분자에 1+s/wp, 1+s/wz, s/wp, s/wz를 바탕으로 pole과 zero를 고려할 수 있다

Asymptotic Bode Plot의 원리를 바탕으로 pole과 zero를 고려할 수 있다

#Capacitor에 의한 폴이 어디서 생성될까?

1.저항과 Capacitor로 인한 Low pass filter 구조

2.저항과 Capacitor의 병렬 구조

Low pass filter에는 pole 1개

High pass filter에는 pole 1개 그리고 s term으로 부터 비롯된 zero at origin이 있다

#Miller Capacitor

Capacitor가 클수록 양단의 전압 차이는 쉽게 변하지 않는다

Capacitor 양단이 모두 ground가 아닐 때, 왼쪽 노드가 증가할 때 오른쪽 노드가 감소한다면 Capacitor는 전압 변화를 싫어하기 때문에 왼쪽 노드를 증가시키기 더욱 어려울 것이다

왼쪽 노드를 증가시키기 어려운 것을 Capacitor가 큰 것으로 고려할 수 있고 이것이 Miller Capacitor의 원리이다

하지만 Miller Capacitor이 Miller 'approximation'이라고 불리는 이유는 Av로 DC gain을 사용하기 때문이다

결과적으로 고주파수에서는 더욱 복잡한 요소가 개입되기 때문에 Miller approximation을 사용하지 않고 저주파수나 중주파수에서 주로 사용한다

#MOSFET의 junction capacitor

아래는 고주파수에서 주로 고려되는 작은 Capacitor인 MOSFET의 junction capacitor이다

#Low/Mid/High Frequency Response

Low frequency response는 큰 Capacitor(coupling cap, bypass cap)에 의해서 결정

High frequency response는 작은 Capacitor(MOS의 junction cap)에 의해서 결정

Low frequency에서 작은 Capacitor들은 임피던스가 매우 커서 open 상태라 고려하지 않는 것이고

High frequency에서 큰 Capacitor들은 임피던스가 매우 작아서 short로 고려되는 것이다

#CS AMP의 frequency response

1.Low frequency

2.High frequency

고주파수에서는 Miller approximation(using DC gain)이 정확하지 않기 때문에 direct analysis를 사용

direct analysis에서는 KCL과 같은 기본적인 방법으로 전달함수를 유도하고 pole은 dominant pole을 고려해서 결정한다

3.Input/Output Impedance

위의 입출력 임피던스는 Gain 구할 때와 다르게 Miller approximation을 사용해서 구했다

Miller effect에 의해서 입력 쪽에서 보이는 Cgd의 크기가 전압이득에 따라서 매우 크다

따라서 전압 이득이 증가한다면 입력 임피던스가 줄어드는 효과도 발생한다

이러한 Miller effect 때문에 고주파수로 갈수록 입력 임피던스가 급격하게 감소하는 현상이 발생한다

이러한 문제는 CG를 cascoding하면 CS의 G에서 D로의 gain을 gm1/gm2로 줄임으로써 해결할 수 있다(뒤의 cascode를 추가한 회로의 frequency response에서 다뤄진다)

#CG AMP의 frequency response

1.Low frequency

CG AMP는 입력 임피던스가 작아서 R_PREV가 영향을 끼친다

2.High frequency

CG AMP에서는 Miller effect가 없다

#SF의 frequency response

1.Low frequency

2.High frequency

SF에서도 direct analysis를 통해서 전달함수를 구했고 dominant pole 방식을 고려해서 dominant pole과 non-dominant pole을 고려할 수 있다

SF의 Output impedance를 살펴보면 인덕터의 impedance와 동일하다(1/Rs<gm)

따라서 인덕터 대신 트랜지스터를 사용해도 된다는 것이다

결론적으로 CS, CG SF AMP 모두 2개의 pole을 가지고 있다

따라서 너무 고주파수에서는 전압이득이 작을 것이다

또한, 주파수에 따라 입력 임피던스와 출력 임피던스도 변화한다

#Cascode를 추가한 CS 증폭기의 frequency response

CS AMP와 CG AMP는 각각의 장단점이 존재한다

이를 결합하면 Miller effect로 인해 고주파수에서 입력 임피던스가 감소해 결과적으로 전압이득이 작아지는 문제를 해결할 수 있다

CS AMP의 전압이득이 커서 고주파수에서 입력 임피던스가 작아지는 것인데 이를 Cascode를 고려함으로써 CS AMP의 전압이득을 줄여 Miller effect로 인한 입력 임피던스의 감소를 막을 수 있다

CS+CG를 통한 최종 전압 이득은 아래와 같다

CS+CG를 통해 얻는 최종 전압이득은 단일 CS AMP 전압이득과 동일하지만 주파수 상승에 따른 입력주파수의 감소를 막는다는 큰 이점이 존재한다

아래는 Cascode를 추가한 CS 증폭기의 입출력 임피던스와 3-pole이다

#차동 증폭기의 frequency response

Half circuit을 고려해 CS AMP와 동일한 방법으로 전달함수의 frequency response를 구할 수 있다

6.피드백

#Feedback system의 기본구조

피드백은 출력을 원하는 방향으로 규제하는 역할을 수행하고 기본구조는 아래와 같다

1) Feedforward system

2) Output sense mechanism

3) Feedback network (K = Xf/Y)

4) Comparison mechanism (Error = X-Xf)

#Feedback system의 장점

피드백의 장점은 아래와 같다

1) Gain이 작아지지만 BW가 커진다(pole이 더 고주파에서 나온다)

2) 선형성이 좋아진다

#Loop gain과 Error의 관계

Loop gain이 클수록, Error는 작아진다

Loop gain이 매우 크다면, Error=0이라서 Xf가 X를 잘 따라간다

또한, Loop gain이 크다면 'X의 변화량이 많더라도' AMP의 input인 'Error의 변화량은 작다'

뿐 만 아니라 closed loop gain이 open loop gain이 아니라 feedback factor에 의존하게 된다

#Loop Gain을 어떻게 측정할 것인가?

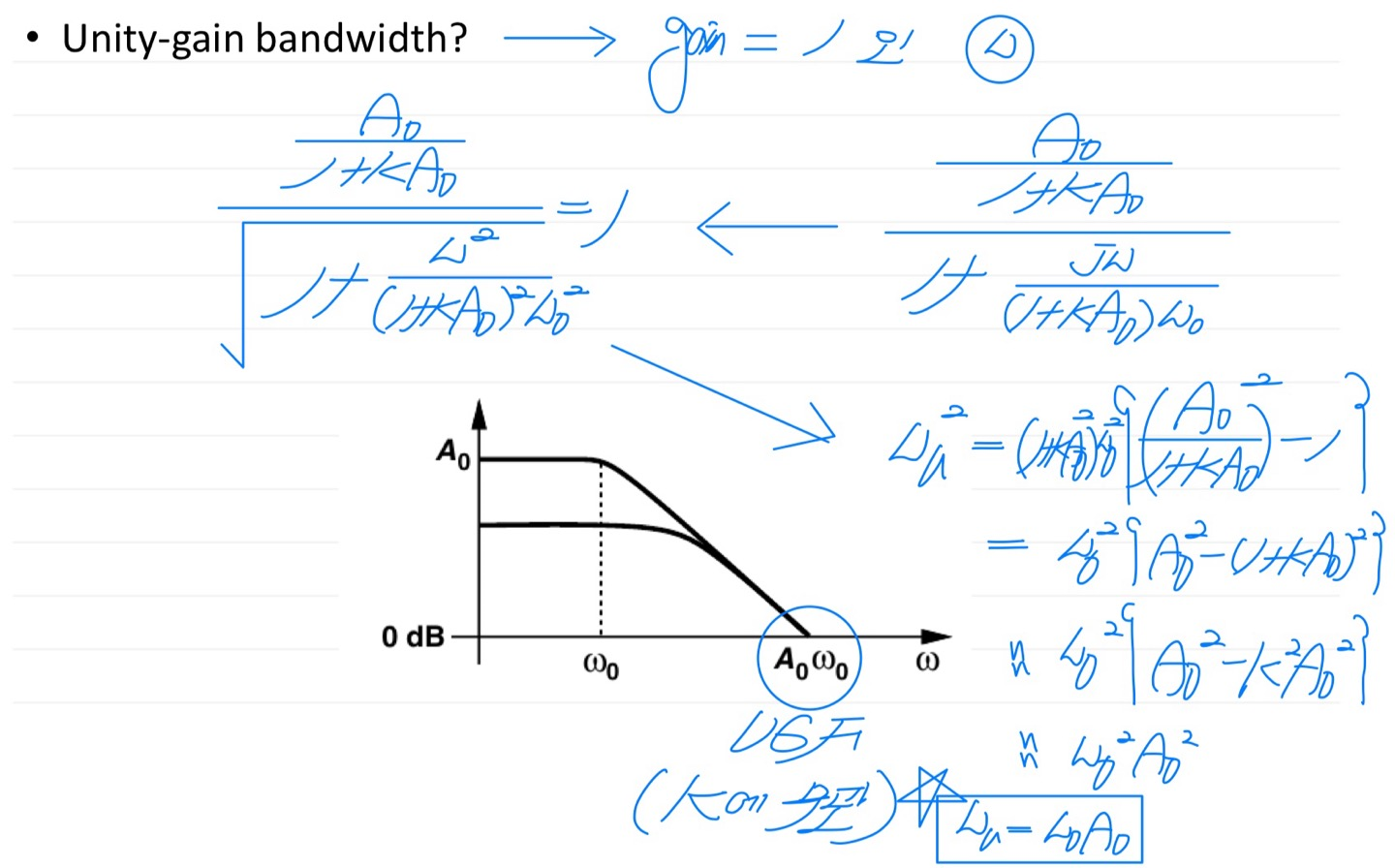

#피드백의 유무에 따른 Bode plot의 차이(1-pole system)

1-pole system에서 UGF는 피드백의 유무와 관계없이 DC gain과 pole의 곱이다

#피드백 Output Sensing을 어떻게 잘할 것인가?

#4가지 증폭기는 어떤 것이 있을까?

왼쪽은 각 증폭기 종류에 따라 이상적인 입출력 임피던스를 표시한 것이다

하지만 입출력 임피던스 경향성을 반드시 해당 증폭기가 따라야 하는 것은 아니다 → sensing과 comparison을 어떻게 하는지에 주목

오른쪽 그림의 파란색 그림은 실제적인 회로를 위한 추가요소를 그린 것이다

#증폭기는 입출력 임피던스에 따라 고정적인 것인가?

CG 증폭기는

입력 임피던스가 작아 전류를 잘 받고(저항이 작으면 전류원의 전류를 다 가져온다)

출력 임피던스가 커서 전류를 잘 준다(저항이 크면 뒷 단에 전류를 다 준다)

따라서 전류 증폭기인데 S → D로 자연스럽게 전류가 흐르므로 Gain은 1이다(전류 버퍼)

왜 사용하는 걸까?

SF 증폭기를 사용하는 것과 같은 내용이다(전압 버퍼)

SF는 입력 임피던스가 커서 앞 단의 출력 저항이 커도 많은 전압을 가져올 수 있고

출력 임피던스는 작아서 뒷 단의 입력 저항이 작아도 많은 전압을 전달 할 수 있다

결국 전압 변화를 키워서 큰 전압 변화를 전달하고자 하는 앞단의 전압 증폭기의 의도를 지켜주려 하는 것

아래는 CG 증폭기이다

CG 증폭기(전류 버퍼)는

입력 임피던스가 작기 때문에 앞 단의 출력 저항이 작아도 많은 전류를 가져올 수 있고

출력 임피던스는 커서 뒷 단의 입력 저항이 커도 많은 전류를 전달 할 수 있다

결국 전류 변화를 키워서 큰 전류 변화를 전달하고자 하는 전류 증폭기의 의도를 지켜주려 하는 것

CG 증폭기는 전류 버퍼 역할뿐만 아니라 아래처럼 큰 Capacitor로 인한 저주파 pole을 형성을 막을 수 있다

Cp가 크다고 가정할 때

왼쪽의 회로는 pole이 저주파에 존재한다

따라서 BW가 작다

이는 RD가 Cp를 막지 못하기 때문이다

만약 Cp와 pole을 만드는 저항이 작다면 Cp가 만드는 pole을 고주파에 위치 시킬 수 있을 것이다

이러한 Cp와 엮이는 저항을 작게 하기 위해서 CG 증폭기를 사용할 수 있다.

즉 CG 증폭기로 한번 끊어주는 것이다

CG 증폭기는 입력 저항이 작으므로 Cp가 만드는 pole을 고주파에 위치시킬 수 있고

출력 쪽의 RD가 만드는 pole은 작은 Capacitor를 부하 단에 추가적으로 위치시켜 저주파 pole이 생기는 것을 막을 수 있다

#Output sensing과 Comparison mechanism을 어떻게 구성할 것인가?

기존 회로에서 어떤 Mechanism을 사용했는지 파악하는 능력을 갖출 필요가 있는 이유는?

피드백의 4가지 일반적인 topology에 대해서 일반화 한 뒤, 실제 회로에서 입력 임피던스와 출력 임피던스를 공식으로 구하면 편리하기 때문이다

sensing과 comparison을 어떻게 하는지에 주목한다면 4가지 피드백 topology 중 어떤 것인지 알 수 있다

#Sensing/Return Voltage/Current

#피드백의 극성

입력의 증가 또는 감소 가정

그에 따른 출력 변화를 본다

피드백이 만드는 출력 변화와 비교한다

피드백이 입력과 다른 출력 변화를 만들면 음의 피드백

또는, Diagram를 바탕으로 회로의 +, - 관계를 통해 알 수도 있다(ex.ERROR AMP의 +입력 → CS AMP(음의 전압 이득) → 음의 피드백)

#Topology에 따른 입출력 임피던스

Topology 종류를 안다면 공식을 이용해 입출력 임피던스를 바로 구할 수 있다

#Feedback Stability

1.Bode plot 기본

2.Feedback stability

Gain crossover가 Phase crossover보다 저주파에 있다면 stable하다

바르크 하우젠 조건은 Feedback이 unstable할 조건이다

아래는 PM을 고려한 1-pole system 설계 과정이다

1.PM 결정 후, -180+PM에서 UGF를 만든다

2.1-pole system이기 때문에 -20dB/dec를 고려해 올린다

3.DC gain과 만나는 지점이 pole이다

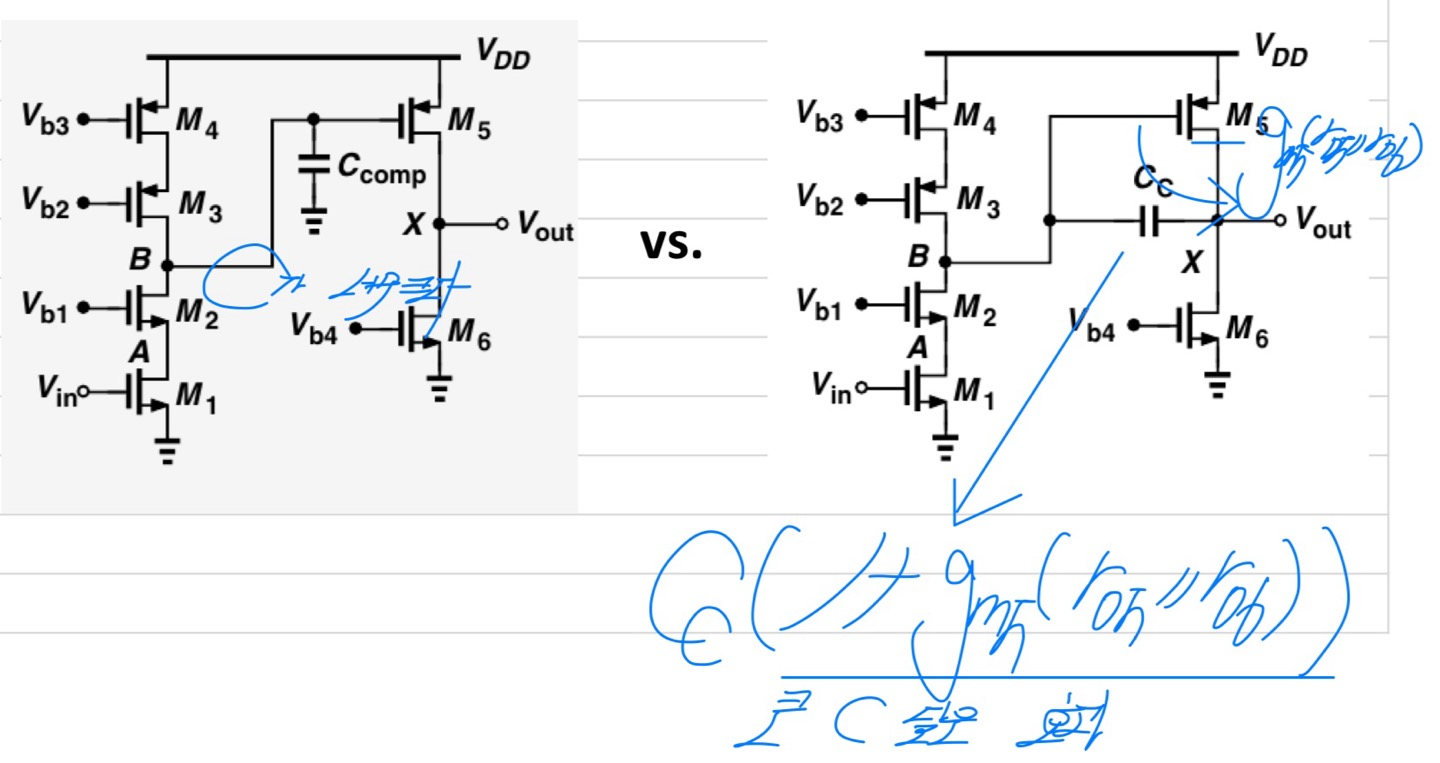

아래는 Compensation을 위해 Miller Capacitor를 사용하는 이유이다

왼쪽 그림에서 A, B, OUT node 중에서 B가 dominant pole인데

dominant pole을 저주파로 보내 Compensation을 하고 싶다면

큰 Capacitor를 달아주면 된다

이러한 큰 Capacitor는 오른쪽의 Miller Compensation을 통해서 더 작은 Cap으로 매우 큰 Capacitor를 단 효과를 만들 수 있다

'전자회로' 카테고리의 다른 글

| URP(FVF LDO) (0) | 2024.11.18 |

|---|