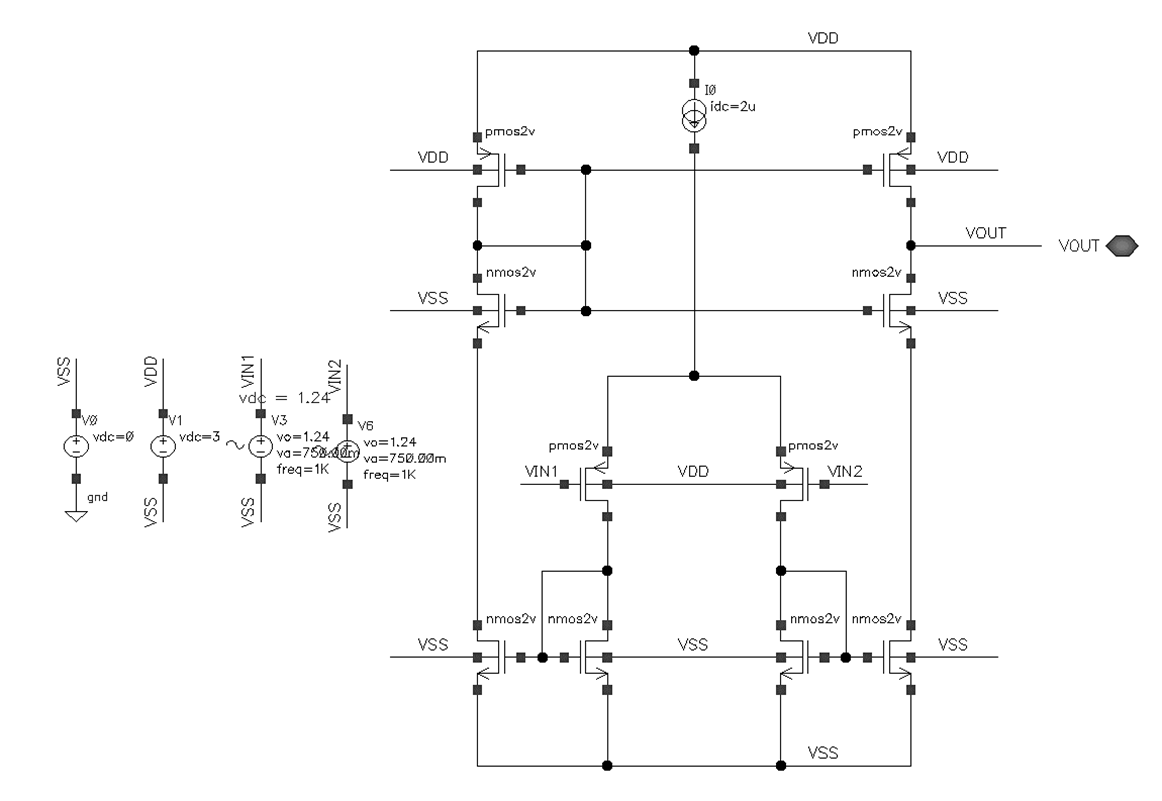

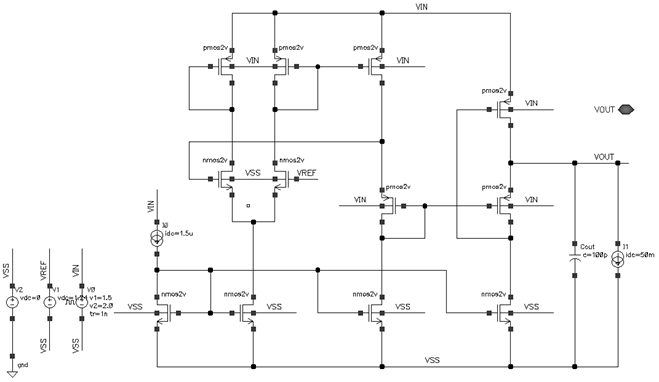

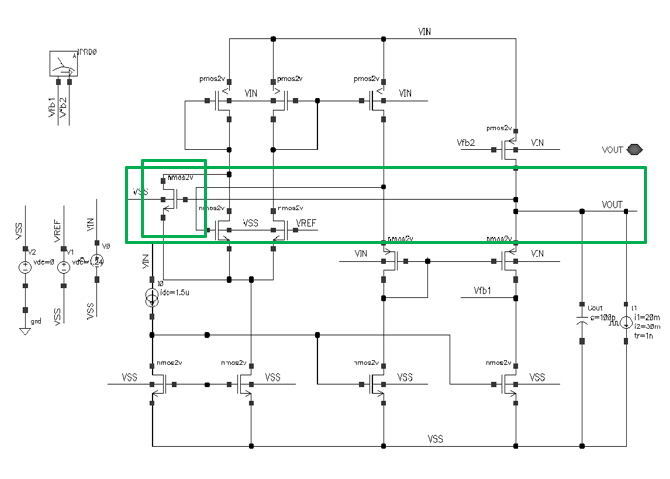

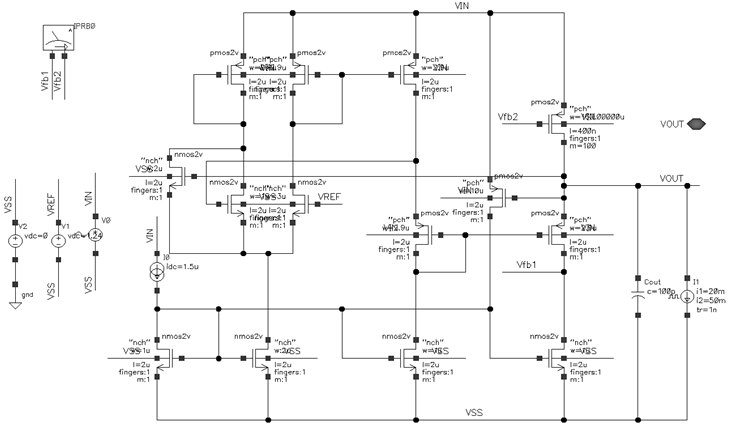

1.기본 LDO

Error Amp 설계 → 성능 지표에 중요한 역할

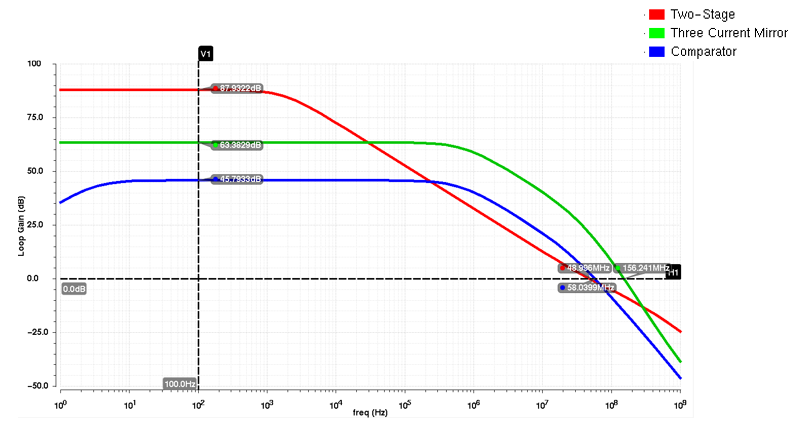

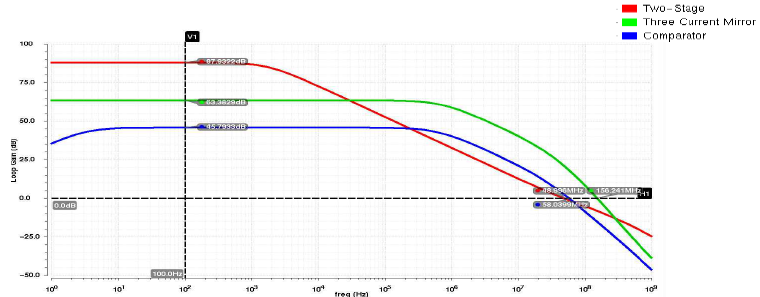

Error Amp로는 2 stage op-amp / current mirror OTA / comparator 사용

이 Comparator 구조는 이후 FVF LDO를 설계할 때 Control Voltage Generation Circuit에서 사용되는 구조이다.

GBW : Current Mirror > Comparator > 2 Stage op-amp

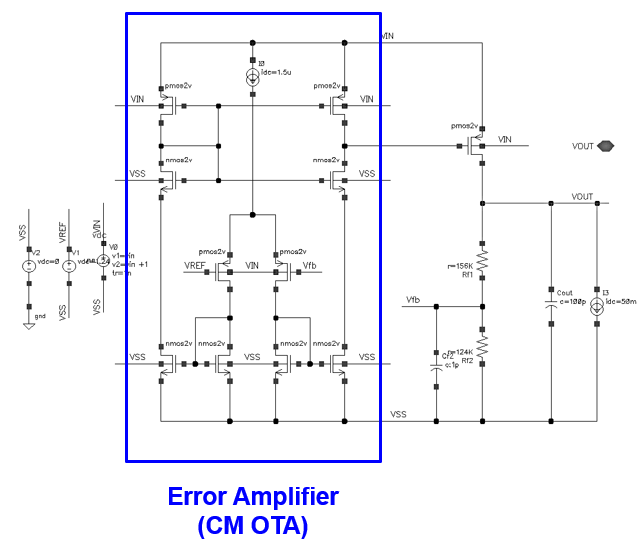

따라서 GBW가 가장 좋은 Current Mirror를 기본 LDO의 Error Amp로 사용하기로 했다.

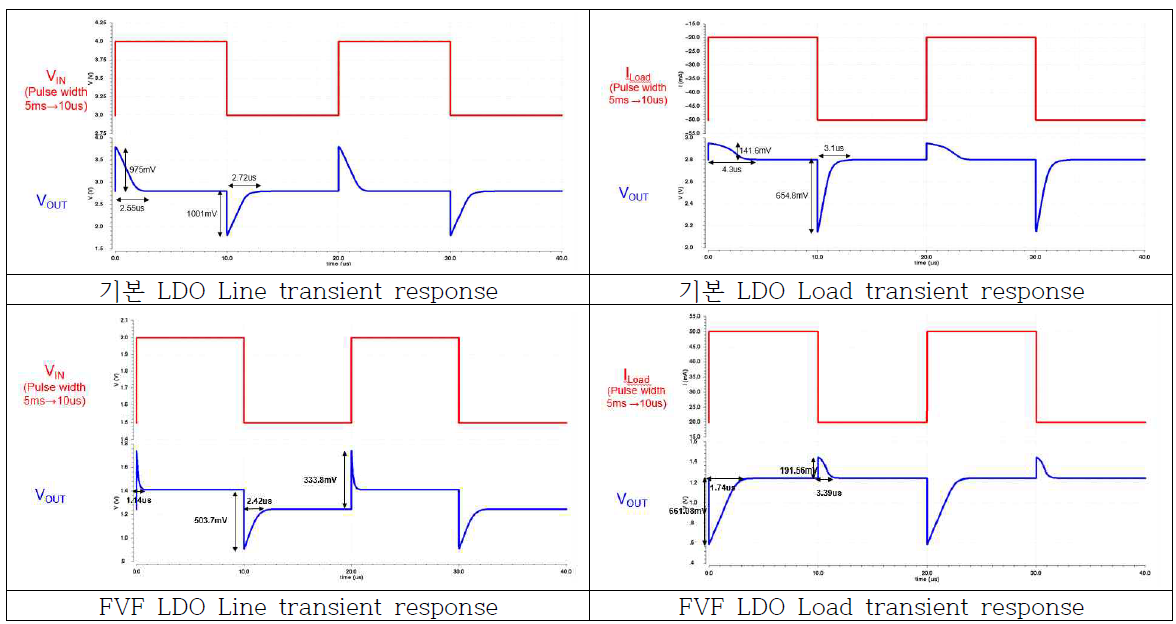

기본 LDO를 설계한 이유는 기본 LDO의 성능지표와 이후 FVF LDO의 성능지표를 비교하기 위함이다.

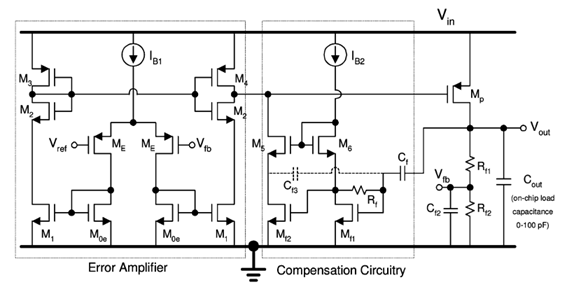

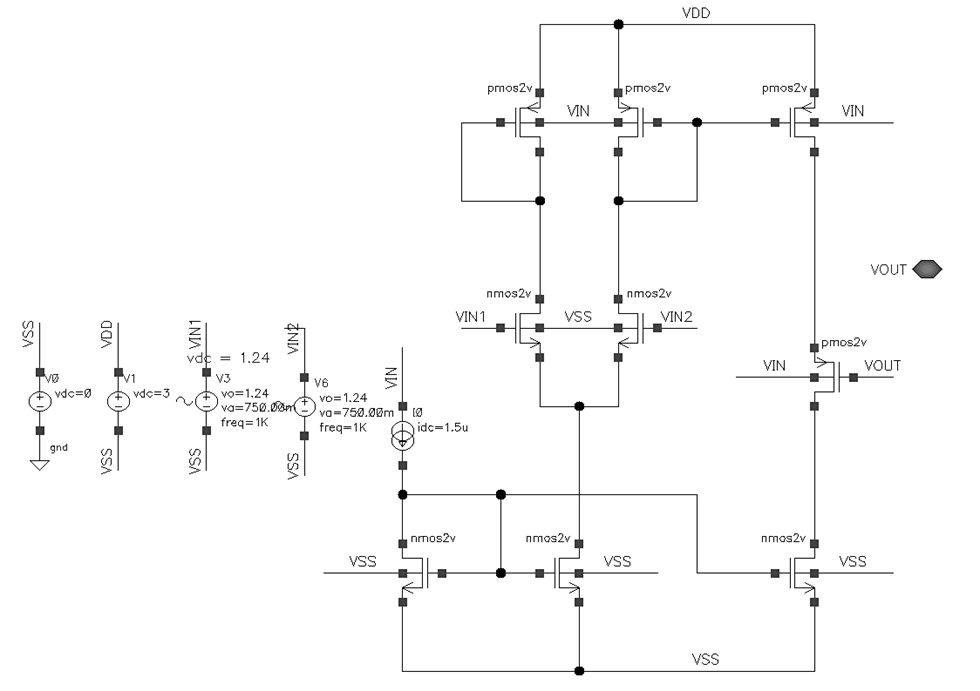

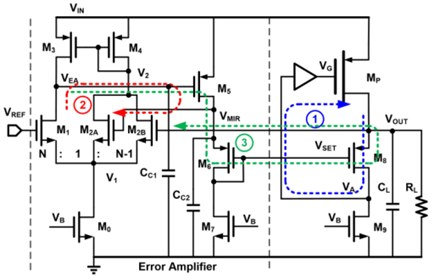

2.FVF(Flipped Voltage Follower) LDO

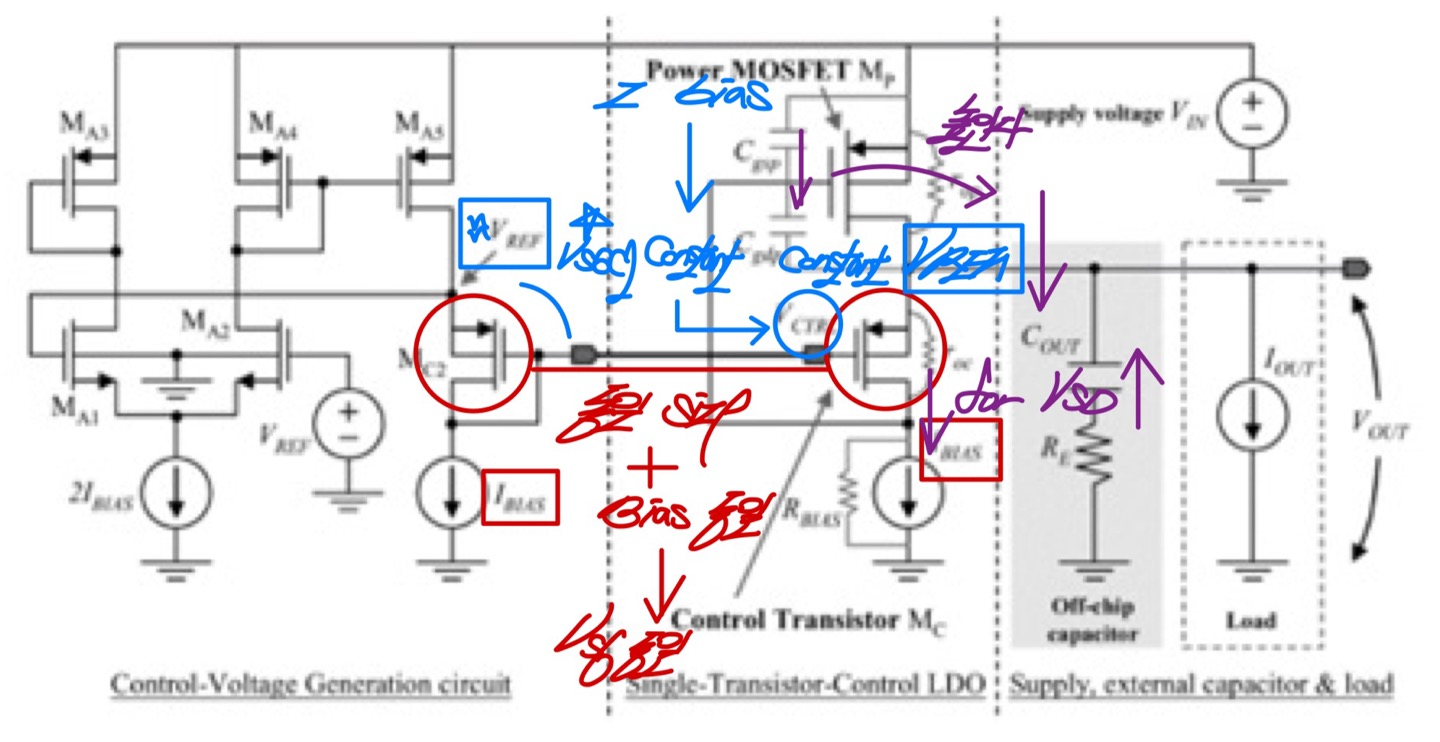

결과적으로, Control-Voltage Generation circuit에서는 말 그대로 일정한 Control-Voltage를 만든다.

이 일정한 Control-Voltage(Vctrl)는 VOUT에서 VREF를 만든다.

(VREF-Vsgc2=Vctrl, Vctrl+Vsgc=Vout, Vsgc2=Vsgc → Vout = VREF)

Steady State 상황은 아래와 같다.

1.VREF 설정.

2.IBIAS를 결정함으로써 IBIAS를 만들기 위한 Vsgc2가 결정된다.

3.VREF와 IBIAS는 상수이므로, Vctrl은 constant이다. 또한, Vsg2도 constant이다.

4.Control Transistor Mc의 size가 Mc2와 같고, IBIAS가 같으므로 Vsgc는 Vsgc2와 동일하다.(Steady state에서)

5.따라서 VOUT은 VREF와 같다.(Steady State에서)

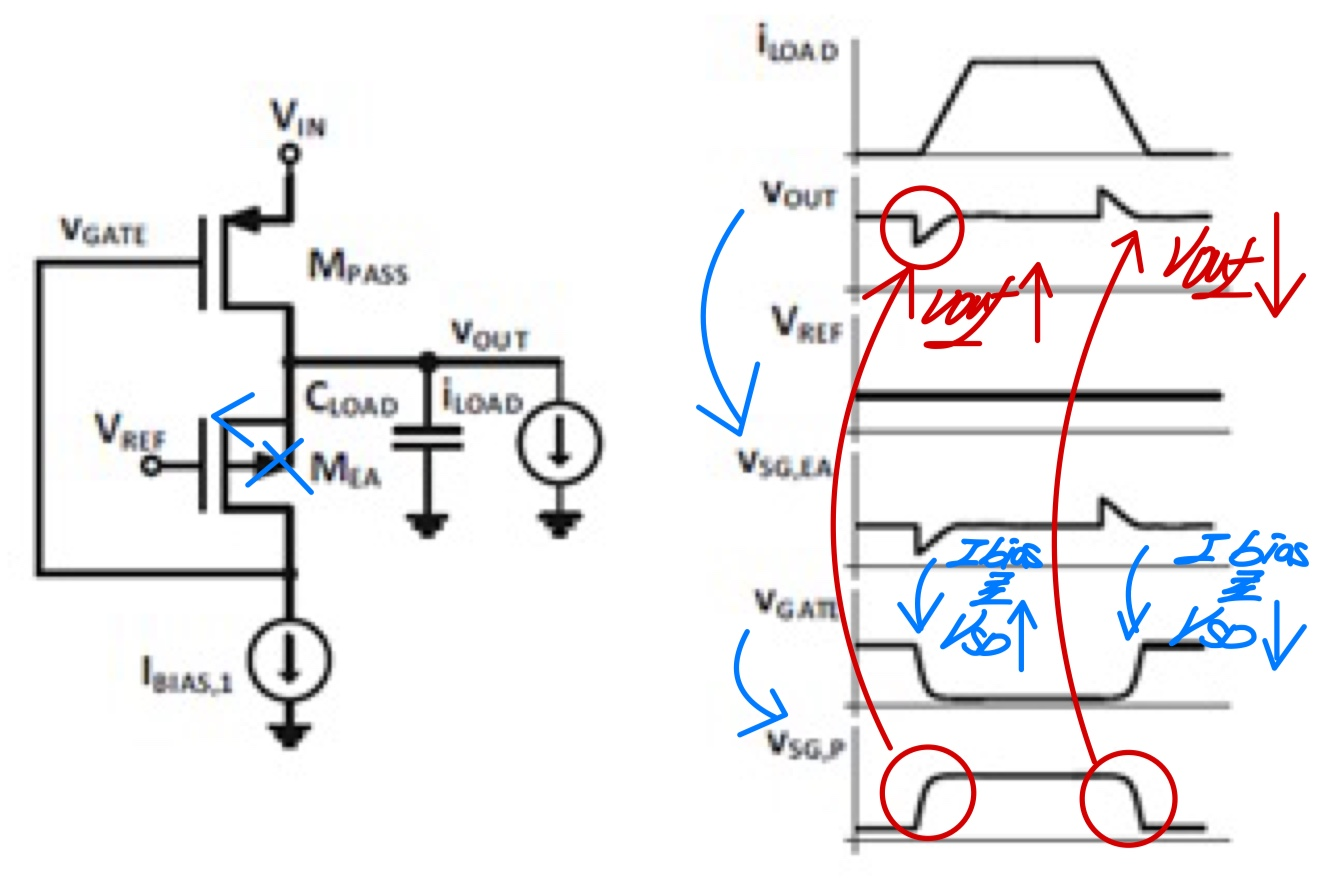

이후 load 조건이 변한다면(VOUT이 변한다면),

IBIAS는 고정이므로, Vsgc의 변화에 따라서 Vsdc가 변하게 된다.

이러한 Vsdc는 pass tr의 gate 전압에 반영이되어

Regulation을 수행하게 된다.

이는 fast loop를 구성해, 기본 LDO보다 빠른 transient response를 만들어낸다.

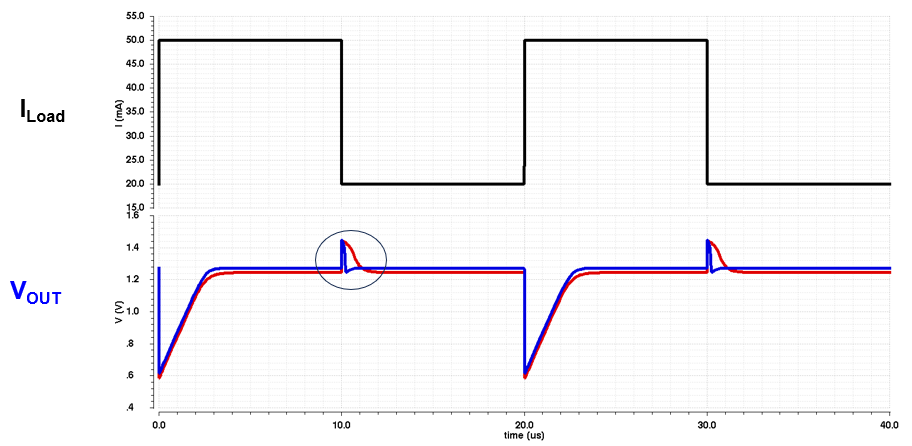

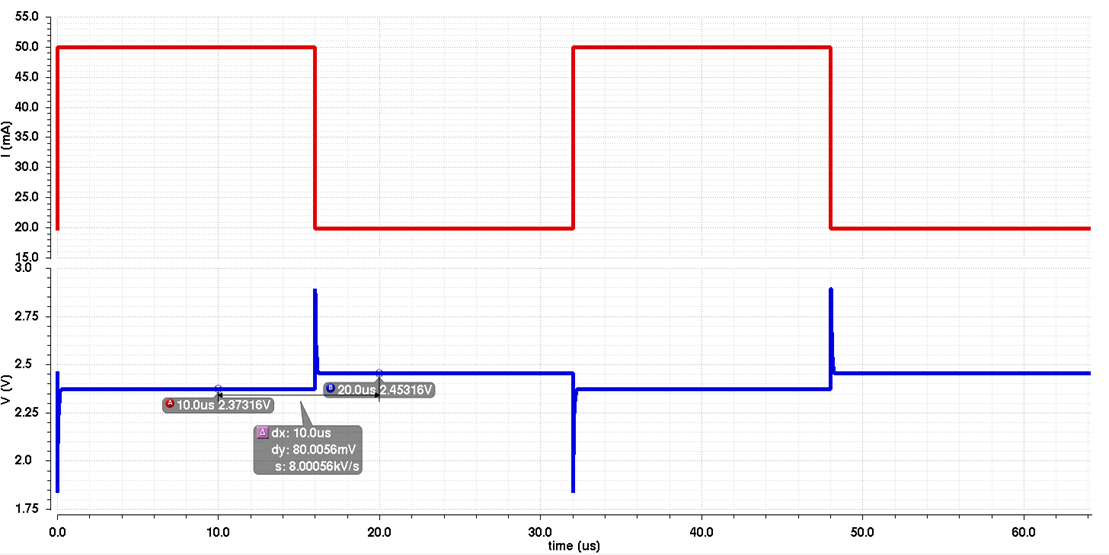

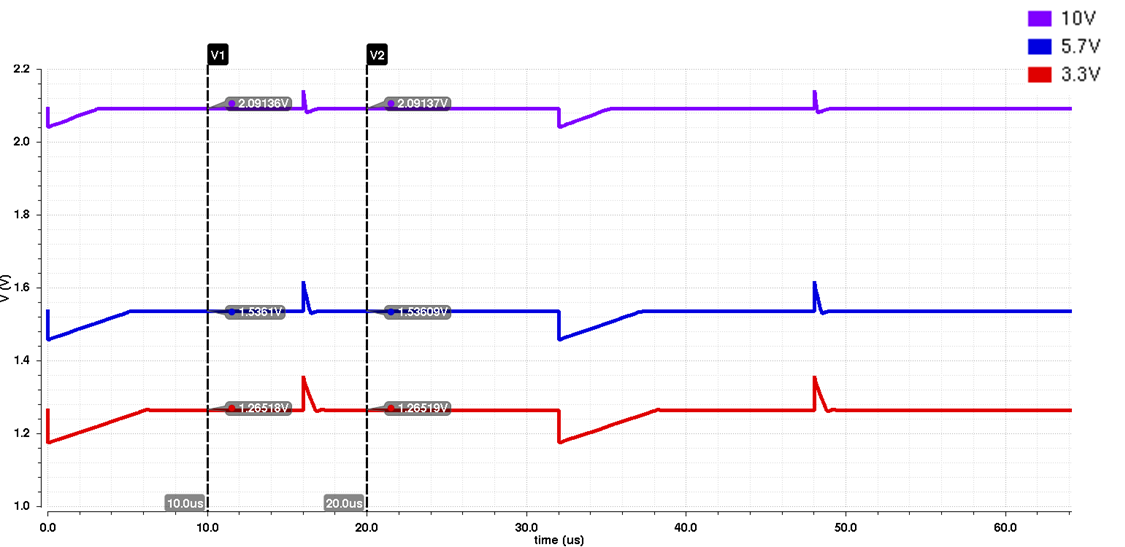

transient speed가 상당히 좋아진 것을 확인할 수 있다.

3.성능 향상을 위한 노력

설계한 FVF LDO를 추가적으로 개선한 것들을 다뤄보겠다.

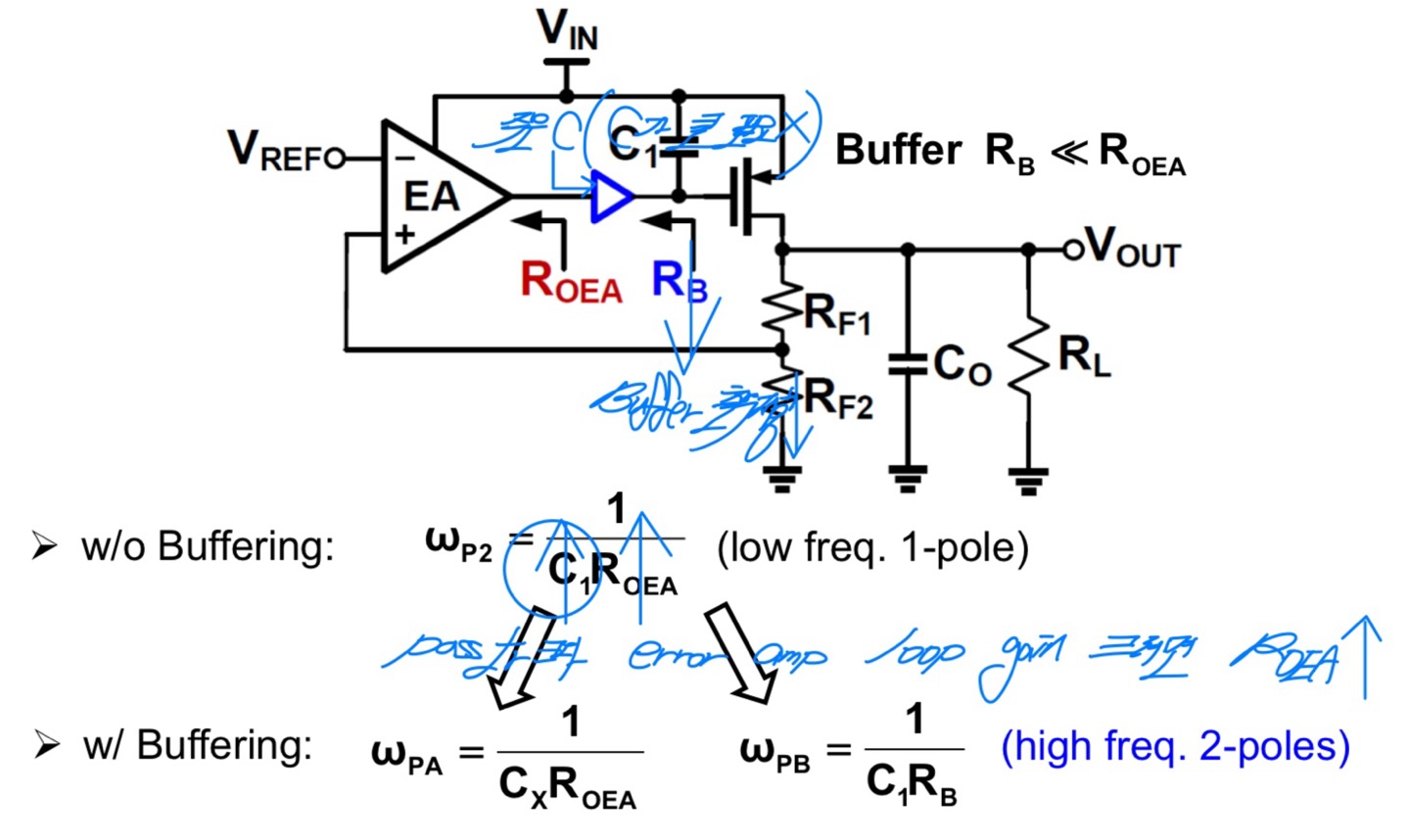

1.Buffer(사용X)

Stability 확보를 위해 Buffer를 활용한 Impedance Attenuation

LDO 대부분에서 Impedance Attenuation Buffer를 사용한다.

Buffer를 사용해 한개의 저주파 pole을 두개의 고주파 pole로 만든다.

이를 통해 FVF LDO의 대역폭을 넓히고자 했고, FVF LDO가 빠르게 변하는 부하 조건에 신속하게 대응할 수 있도록 설계하려 함.

2.Slew-Rate Enhancement(SRE) 구조 추가

Steady state에서는 subthreshold 영역에서 동작하므로 전력소모가 매우 작고(거의 동작하지 않는다),

출력전압 undershoot 상황에서 turn on 되어 전류를 생성해 전압을 원상복구 시키는 역할을 한다.

이 또한, Fast loop이다.

Slow loop는 전체 피드백을 돌아서 오는 loop이다.

기존 FVF와 유사하면서도 출력전압 undershoot 상황에서 transient response가 향상되었다.

3.Additional loop 추가

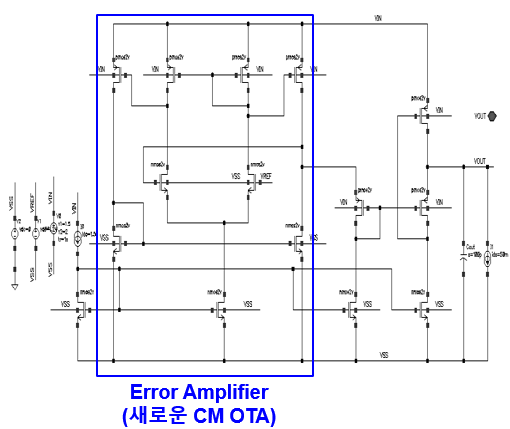

Error amplifier단에서 MOS의 Gate전압으로 전압을 sensing해, VOUT로 직접 연결해 새로운 loop를 만들었다.

빠른 속도로 출력 전압을 잡아주도록 Loop를 형성.

기존 FVF와 유사하면서도 출력전압 overshoot 상황에서 transient response가 향상되었다.

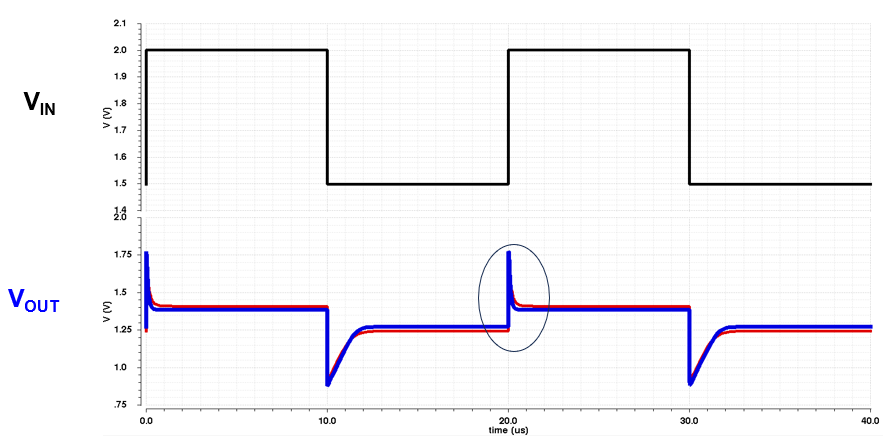

4.최종모델

VOUT 증가/감소에 상관없이 목표했던 대로 Transient speed가 매우 향상된 LDO를 만들 수 있었다.

하지만 아래와 같은 문제점을 발견했고, 최종모델에서 고려하기에는 너무 복잡해져 기본 FVF LDO에서 실험을 진행했다.

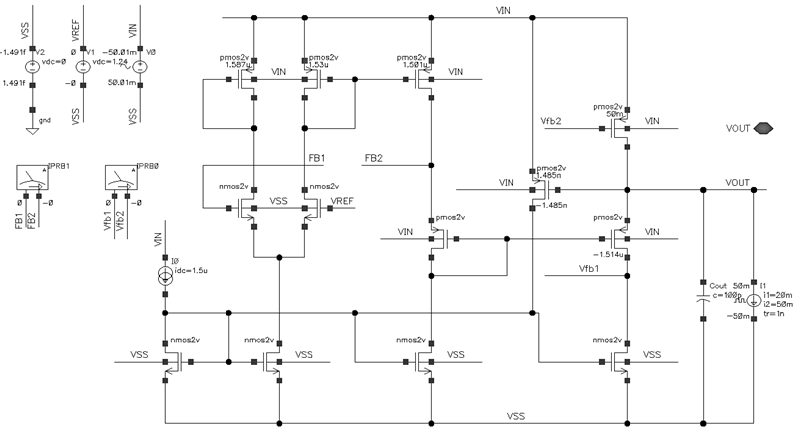

4.기본 FVF LDO에 대한 문제점 개선

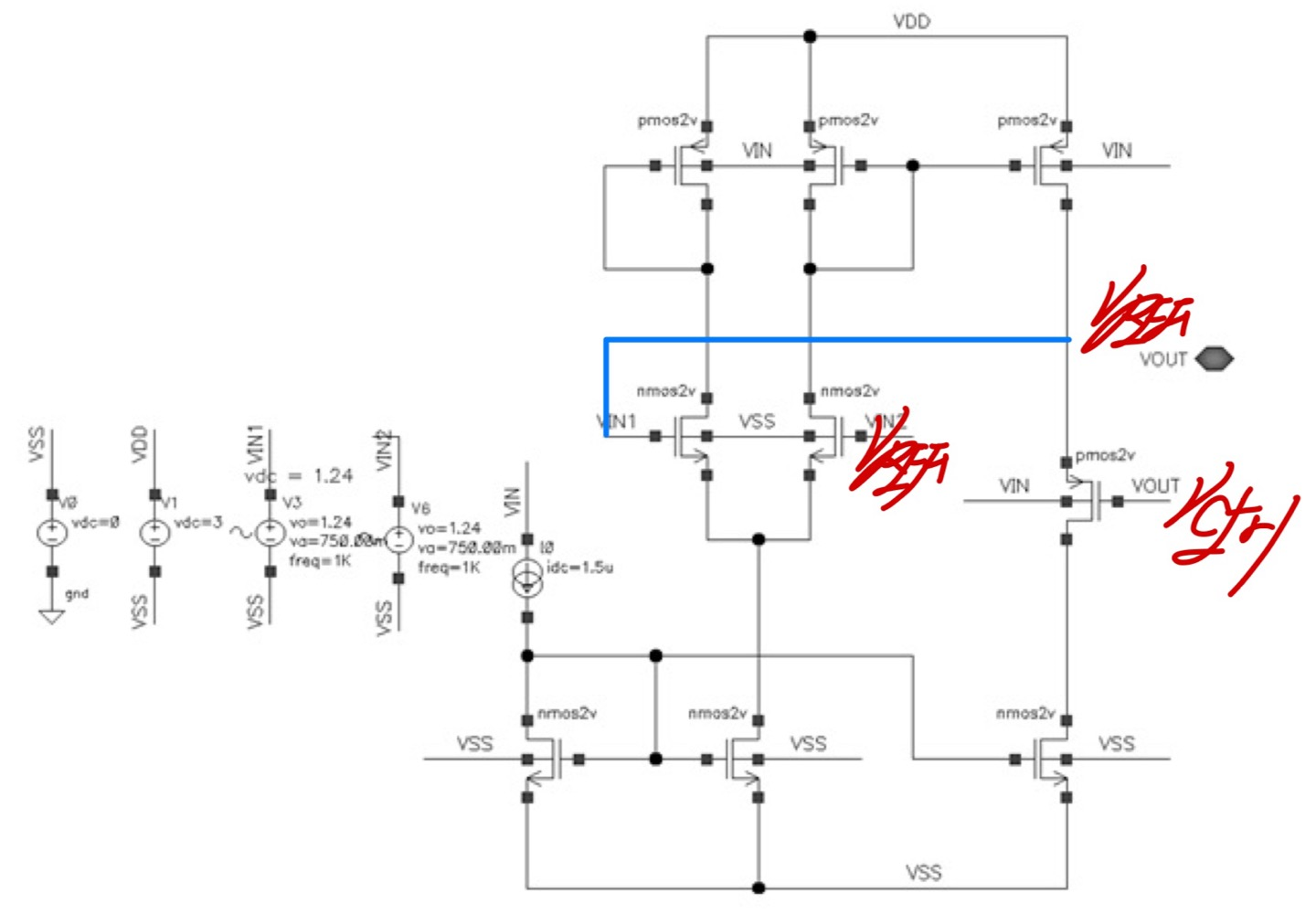

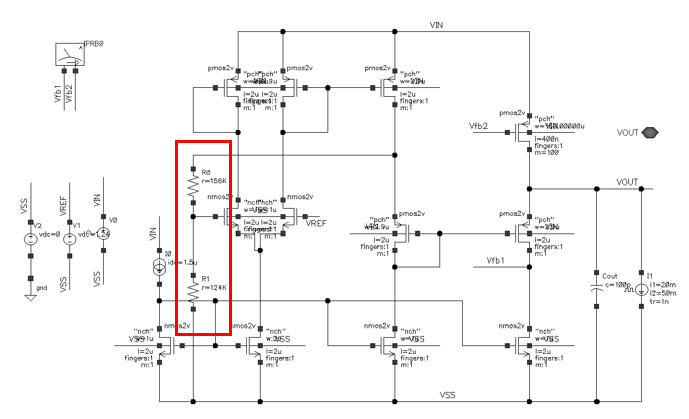

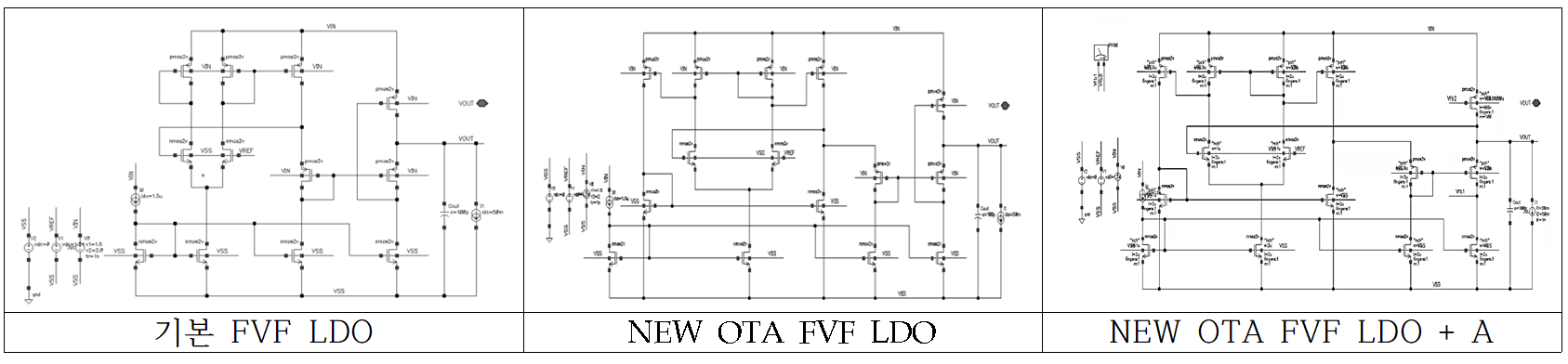

1.Output Voltage Dynamic Range

기본 LDO는 피드백 저항을 변경함으로써 출력 전압을 변화시킬 수 있었다.

하지만 FVF LDO는 피드백 저항으로 출력 전압을 결정하는 구조가 아니라서 출력 전압 변경에 한계가 존재했다.

기본 LDO가 피드백 저항으로 출력 전압을 바꾸는 방식에 착안하여, Error Amp 단에 전압 divider를 이용해 출력전압을 조정함.

출력 전압 기준이 VREF(1.24V)였는데, 전압 divider를 사용해 출력전압을 변경했다.

빨간색 네모안의 MOSFET gate전압은 VREF이므로 전압 divider에 의해 전압을 더 높임으로 Vctrl를 더 높일 수 있고, 결과적으로 출력 전압 기준을 높일 수 있다.

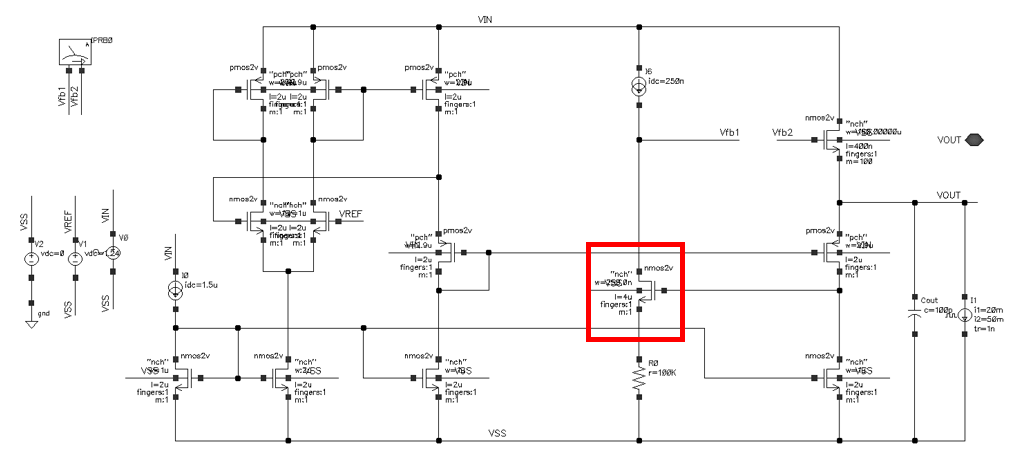

2.Wide Input

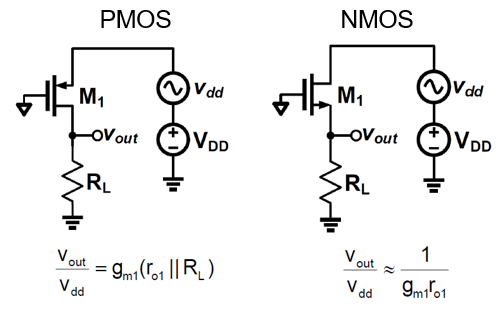

Wide Input을 위해 pass tr을 pmos에서 nmos로 변경했다.

이는 pmos는 input voltage가 vgs에 영향을 끼치지만 nmos는 vds에 영향을 끼치는 것을 고려한 것이다.

saturation 전류식을 고려해보았을 때 vds가 vgs보다 덜 dominant하기 때문에, 더 높은 input voltage까지 동작영역을 유지할 수 있다.

또한, pass tr을 nmos로 변경했으므로 negative feedback을 유지하기 위해 nmos를 활용한 cs amp를 추가했다.

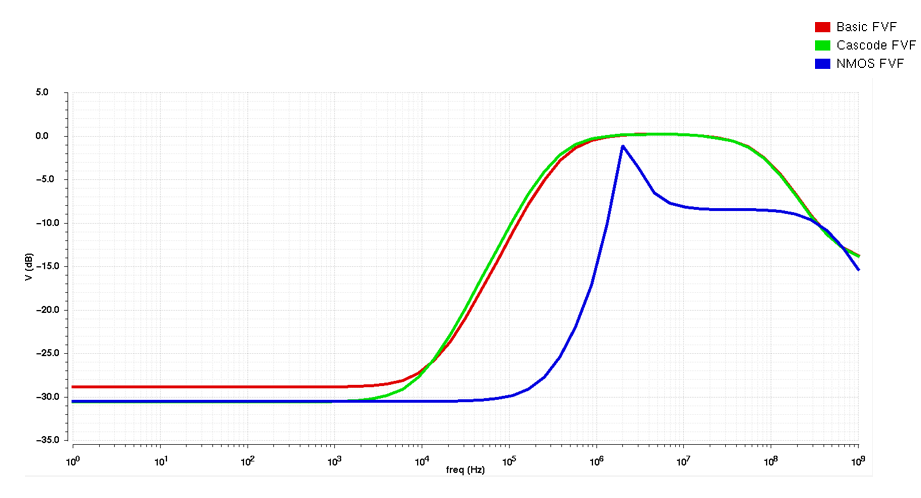

pmos pass tr을 사용했을 때는 input voltage 1.8V까지 출력 전압 기준 1.25V를 유지했고,

nmos pass tr을 사용했을 때는 input voltage 3.3V까지 출력 전압 기준 1.25V를 유지했다.

이후로는 몇몇 tr들이 Saturation이 아닌 영역에 존재해 출력 전압 기준 1.25V를 유지하지는 못했지만, regulation이 이루어지는 것은 확인했다.

3.PSRR 개선

1)저주파 PSRR

FVF LDO에 사용된 Comparator 구조가 다른 Error Amp에 비해서 DC gain이 작은 것을 확인할 수 있다.

이러한 Error Amp의 DC gain을 높일 수 있다면, 저주파에서 PSRR을 개선할 수 있을 것이다.

2번째의 NEW OTA FVF LDO는 Error Amp만 새로운 CM OTA로 변경한 것이고

3번째 것은 Error Amp가 전달하는 VREF를 VOUT에 직접 연결한 것으로, Vctrl을 형성하기 위해 거치는 source degenerated CS AMP를 거치지 않기 때문에 전압이득이 높아 저주파 PSRR이 높게 측정된 것으로 판단된다.

2)고주파 PSRR

pass tr로 nmos를 사용하면 pmos를 사용했을 때에 비해 power supply 변화에 따른 출력 전압의 변화를 줄일 수 있다.

따라서 pass tr로 nmos를 사용해 고주파에서 PSRR을 개선했다.